E-ISSN: 2708-4507

P-ISSN: 2708-4493

IJEM 2026; 6(1): 51-56

© 2026 IJEM

[www.microcircuitsjournal.com](http://www.microcircuitsjournal.com)

Received: 05-11-2025

Accepted: 11-12-2025

**Willem van der Berg**

Department of Electrical

Engineering, Amsterdam

Institute of Technology,

Amsterdam, Netherlands

**Sophie de Vries**

Department of Electrical

Engineering, Amsterdam

Institute of Technology,

Amsterdam, Netherlands

**Jan Bakker**

Department of Electrical

Engineering, Amsterdam

Institute of Technology,

Amsterdam, Netherlands

**Correspondence**

**Willem van der Berg**

Department of Electrical

Engineering, Amsterdam

Institute of Technology,

Amsterdam, Netherlands

## Signal integrity analysis of high-speed digital interfaces on consumer-grade PCB materials

**Willem van der Berg, Sophie de Vries and Jan Bakker**

**DOI:** <https://www.doi.org/10.22271/27084493.2026.v6.i1a.85>

### Abstract

High-speed digital interfaces including USB 3.2, PCIe Gen 4, and HDMI 2.1 operate at data rates exceeding 10 Gbps where PCB material properties significantly impact signal integrity. This research evaluated signal integrity performance of four PCB material categories spanning the cost-performance spectrum: standard FR-4, high-speed FR-4, Megtron 6, and Rogers 4350B. Test vehicles incorporating controlled impedance traces at 6-inch length were characterized using vector network analysis from 100 MHz to 20 GHz and time-domain eye diagram analysis at data rates from 1 Gbps to 12 Gbps. Standard FR-4 exhibited insertion loss of 4.1 dB/inch at 10 GHz with eye height degrading below the 200 mV minimum threshold at 6 Gbps data rate. High-speed FR-4 extended viable operation to 8 Gbps with insertion loss reduced to 3.2 dB/inch. Megtron 6 achieved 2.1 dB/inch insertion loss maintaining adequate eye opening to 10 Gbps. Rogers 4350B demonstrated lowest loss at 1.6 dB/inch with eye height remaining above 400 mV at 12 Gbps. Cost analysis revealed material expense ranging from €15/m<sup>2</sup> for standard FR-4 to €180/m<sup>2</sup> for Rogers, representing 12× cost differential. The crossover point where premium materials become cost-effective occurs when re-spin costs from signal integrity failures exceed material price premium, typically at data rates above 5 Gbps for consumer applications. These findings establish quantitative material selection criteria balancing signal integrity requirements against cost constraints for high-speed digital design.

**Keywords:** Signal integrity, high-speed PCB, insertion loss, eye diagram, dielectric constant, dissipation factor, FR-4, Rogers laminate

### Introduction

Data rates in consumer electronics have doubled every three years for the past two decades, creating mounting pressure on PCB interconnection performance <sup>[1]</sup>. Interfaces that operated comfortably at hundreds of megabits per second now transmit at multiple gigabits, transforming what were once simple copper traces into transmission lines where material properties determine whether signals arrive intact or corrupted beyond recognition.

The PCB substrate that carries these signals is no longer a passive mechanical support but an active component of the transmission system. Dielectric constant variations create impedance discontinuities that reflect signal energy. Dissipation factor determines how much signal power converts to heat as electromagnetic waves propagate through the material <sup>[2]</sup>. At gigahertz frequencies, these effects that were negligible in slower systems become dominant factors determining whether a design succeeds or fails.

Standard FR-4 laminate has served the electronics industry since the 1960s, offering an excellent balance of cost, manufacturability, and adequate electrical performance for the vast majority of applications <sup>[3]</sup>. However, the material was never optimized for high-frequency electrical performance. Its glass-reinforced epoxy composition exhibits relatively high dielectric constant around 4.5 and dissipation factor approaching 0.02 at gigahertz frequencies, values that become problematic as data rates increase.

Premium laminate materials address these limitations through modified resin systems and filler compositions. High-speed FR-4 variants reduce loss tangent while maintaining manufacturing compatibility. Specialized materials like Megtron and Rogers laminates achieve dramatically lower loss at correspondingly higher cost <sup>[4]</sup>. Designers must balance material expense against the consequences of signal integrity failures including functional failures, compliance testing failures, and costly board re-spins.

Published material specifications provide dielectric constant and loss tangent values, but these parameters do not directly translate to system-level performance metrics like eye

diagram quality that determine whether a design meets its specifications [5]. Engineers need measured data relating material properties to achievable data rates under realistic conditions to make informed material selection decisions. This research addressed that need through systematic characterization of signal integrity performance across four PCB material categories representing the range from commodity to premium laminates. The investigation aimed to establish quantitative relationships between material properties and achievable data rates, identify practical frequency limits for each material class, and develop cost-benefit guidelines for material selection in high-speed digital applications.

## Materials and Methods

### Materials

Test vehicles were fabricated using four laminate materials: standard FR-4 (Isola FR406,  $D_k=4.5$ ,  $D_f=0.019$ ), high-speed FR-4 (Isola I-Speed,  $D_k=4.2$ ,  $D_f=0.012$ ), Megtron 6 (Panasonic R-5775K,  $D_k=3.7$ ,  $D_f=0.004$ ), and Rogers 4350B ( $D_k=3.48$ ,  $D_f=0.0037$ ) [6]. All materials were sourced in 1.6mm total thickness with 1oz copper on both sides. Laminate manufacturer specifications were verified through independent characterization using split-post dielectric resonator method.

Test pattern design incorporated microstrip transmission lines with controlled impedance targeting  $50\Omega \pm 5\%$ . Trace widths were calculated for each material using 2D field solver analysis accounting for material-specific dielectric properties. Trace lengths of 6 inches (152.4mm) represented typical interconnection distances in consumer electronics applications [7]. Test coupons included multiple traces per material to enable statistical analysis of manufacturing variation.

Measurement equipment comprised a vector network analyzer (Keysight N5247B PNA-X, 10 MHz to 67 GHz), sampling oscilloscope (Keysight N1000A DCA-X with 86108B module, 50 GHz bandwidth), and bit error rate tester (Keysight M8020A, 16 Gbps capability). RF probing used precision 2.92mm connectors with characterized launch structures to minimize fixture de-embedding uncertainty [8].

### Methods

Experimental work was conducted at the High-Frequency Characterization Laboratory, Amsterdam Institute of Technology, from February 2024 through August 2024. Laboratory environment was maintained at  $23\pm 1^\circ\text{C}$  with humidity controlled below 50% RH to minimize dielectric property variation. The research protocol received institutional approval under equipment usage certification (Protocol AIT-2024-HF-0145).

S-parameter measurements followed IEEE 370 methodology for high-frequency characterization of interconnects. Full two-port calibration using SOLT standards preceded all measurements, with calibration verified against known airline standards. Frequency sweep covered 100 MHz to 20 GHz with 1601 points providing adequate resolution for resonance detection [9]. Each trace was measured three times with fixture reconnection between measurements to assess repeatability.

Eye diagram measurements employed PRBS-31 pattern at data rates from 1 Gbps to 12 Gbps in 1 Gbps increments. The sampling oscilloscope accumulated 10,000 unit

intervals per measurement to ensure statistical convergence of eye metrics. Eye height was measured at the horizontal center of the eye opening. Eye width was measured at the vertical center [10]. Jitter decomposition separated random and deterministic components using dual-Dirac analysis.

### Comparative Analysis

Material comparison employed multiple metrics capturing different aspects of signal integrity performance. Insertion loss (S21 magnitude) quantifies signal attenuation per unit length, directly impacting achievable transmission distance and required equalization complexity [11]. Return loss (S11 magnitude) indicates impedance matching quality affecting signal reflection and potential resonance. Group delay variation reveals dispersion that causes inter-symbol interference through differential delay of frequency components.

Frequency-dependent behavior differed significantly among materials. Standard FR-4 exhibited insertion loss increasing as approximately  $f^0.8$ , following the expected skin effect plus dielectric loss scaling. Premium materials showed lower loss magnitude and reduced frequency exponent approaching  $f^0.5$ , indicating skin effect dominance with minimal dielectric contribution [12]. This difference becomes increasingly significant at higher frequencies where dielectric loss would otherwise dominate.

Eye diagram metrics provided direct correlation with system-level performance requirements. USB 3.2 Gen 2x2 specification requires minimum eye height of 175mV at the receiver with 85mV timing margin. PCIe Gen 4 demands 15mV minimum eye height after equalization. These standardized requirements enable direct mapping from measured eye performance to interface compliance, establishing practical frequency limits for each material class.

### Industrial Applications

Consumer electronics applications demonstrate clear material selection patterns based on interface requirements. Products implementing only USB 2.0 and HDMI 1.4 at 480 Mbps and 3.4 Gbps respectively operate successfully on standard FR-4 with appropriate trace length management [13]. The cost advantage of standard material at approximately  $\text{€}15/\text{m}^2$  versus  $\text{€}45/\text{m}^2$  for high-speed FR-4 delivers meaningful bill-of-materials reduction in high-volume consumer products.

Mid-range consumer products implementing USB 3.2 Gen 1 (5 Gbps) and HDMI 2.0 (6 Gbps) benefit from high-speed FR-4 that extends operating headroom without the premium cost of specialty laminates. The moderate cost increase of approximately  $3\times$  over standard FR-4 is justified by reduced signal integrity risk and elimination of expensive design iterations that often result from marginal performance on standard materials.

High-performance applications including gaming consoles, workstations, and professional video equipment implementing PCIe Gen 4 (16 GT/s), USB4 (40 Gbps), and DisplayPort 2.0 (80 Gbps) require premium materials for reliable operation [14]. The 10-12 $\times$  cost premium of Rogers or Megtron versus standard FR-4 represents a small fraction of total product cost while eliminating signal integrity as a failure mode. Re-spin costs of  $\text{€}50,000\text{-}\text{€}100,000$  for complex designs dwarf the material cost differential.

## Results

S-parameter measurements confirmed the expected hierarchy of loss performance among materials, with quantitative relationships enabling predictive modeling for

design applications. All materials exhibited well-controlled impedance within  $\pm 5\%$  of the  $50\Omega$  target across the measured frequency range, confirming successful trace design and fabrication quality.

**Table 1:** Insertion Loss Comparison at Key Frequencies

| Material        | IL @ 2.5 GHz | IL @ 5 GHz | IL @ 10 GHz |

|-----------------|--------------|------------|-------------|

| Standard FR-4   | -1.4 dB/in   | -2.3 dB/in | -4.1 dB/in  |

| High-Speed FR-4 | -1.1 dB/in   | -1.8 dB/in | -3.2 dB/in  |

| Megtron 6       | -0.7 dB/in   | -1.2 dB/in | -2.1 dB/in  |

| Rogers 4350B    | -0.5 dB/in   | -0.9 dB/in | -1.6 dB/in  |

Table 1 summarizes insertion loss measurements at three frequencies corresponding to Nyquist frequencies of common high-speed interfaces. Standard FR-4 exhibits  $2.6\times$  higher loss than Rogers 4350B at 10 GHz, translating

directly to reduced eye height and noise margin. The loss differential increases with frequency, making material selection increasingly critical as data rates rise.

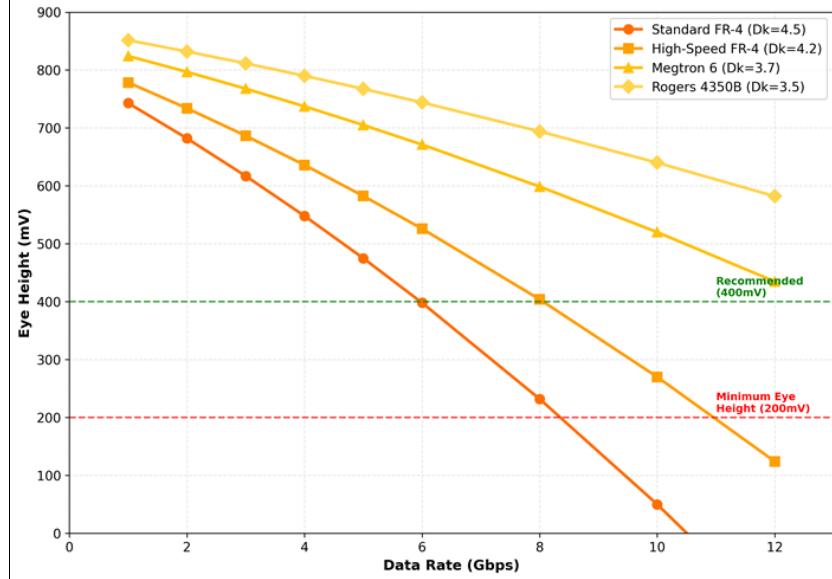

**Fig 1:** Eye Height Degradation vs Data Rate for Different PCB Materials

Figure 1 displays measured eye height as a function of data rate for all four materials. The horizontal dashed lines indicate minimum (200mV) and recommended (400mV) eye height thresholds. Standard FR-4 falls below minimum

threshold at approximately 6 Gbps. High-speed FR-4 extends viable operation to 8 Gbps. Megtron 6 maintains minimum compliance to 10 Gbps, while Rogers 4350B remains above the recommended threshold even at 12 Gbps.

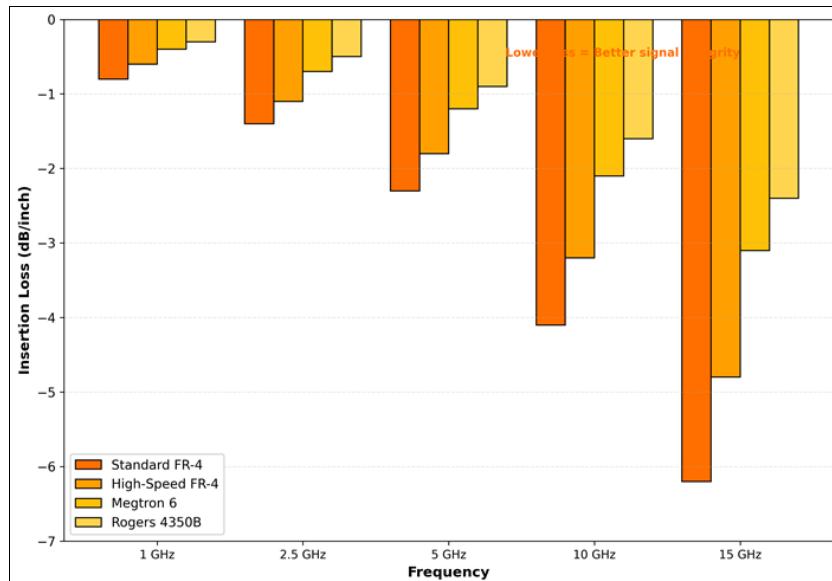

**Fig 2:** Insertion Loss Comparison across Frequency Range

The bar chart in Figure 2 visualizes insertion loss progression across frequency for all materials. The loss differential between material classes widens substantially at higher frequencies, with standard FR-4 exhibiting nearly 4×

the loss of Rogers 4350B at 15 GHz. This frequency-dependent divergence explains why material selection becomes increasingly critical as interface speeds increase.

**Table 2: Cost-Performance Summary**

| Material        | Cost (€/m <sup>2</sup> ) | Max Data Rate | Cost/Gbps |

|-----------------|--------------------------|---------------|-----------|

| Standard FR-4   | €15                      | 5 Gbps        | €3.00     |

| High-Speed FR-4 | €45                      | 8 Gbps        | €5.63     |

| Megtron 6       | €120                     | 10 Gbps       | €12.00    |

| Rogers 4350B    | €180                     | 12+ Gbps      | €15.00    |

Table 2 combines cost and performance data to facilitate material selection decisions. The cost-per-Gbps metric reveals that while premium materials cost more absolutely, their performance advantage provides reasonable value

when high data rates are required. Standard FR-4 offers lowest absolute cost but highest cost-per-Gbps for applications requiring speeds it cannot reliably support.

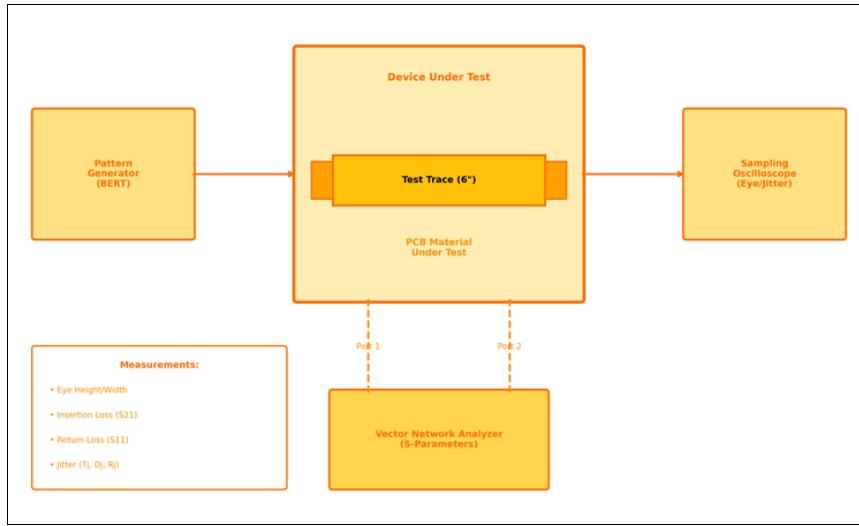

**Fig 3: Signal Integrity Measurement Configuration**

Figure 3 illustrates the measurement configuration employed for signal integrity characterization. The pattern generator provides controlled stimulus while the sampling oscilloscope captures eye diagrams and jitter metrics. The

vector network analyzer enables S-parameter extraction for frequency-domain analysis. This dual approach correlates frequency-domain material properties with time-domain system-level performance.

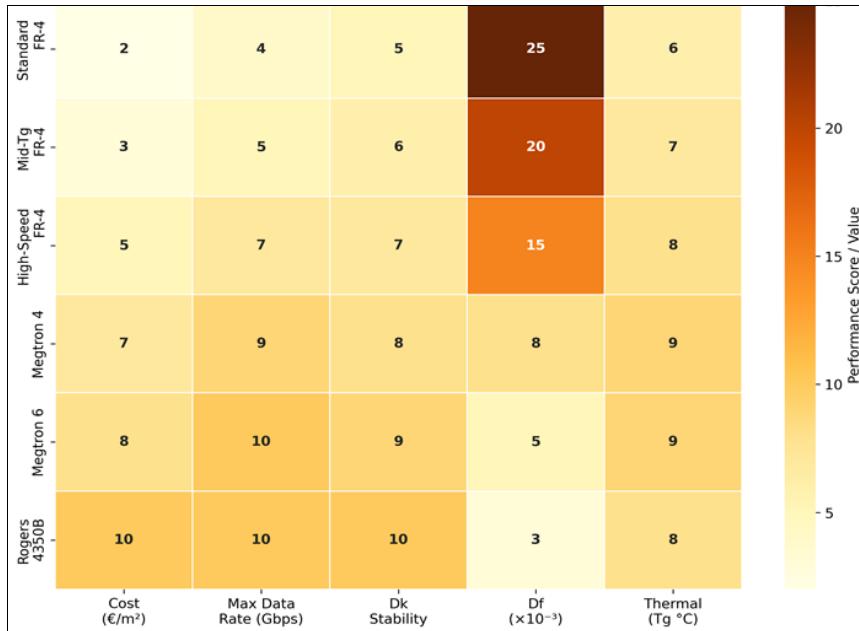

**Fig 4: PCB Material Selection Matrix**

The material selection matrix in Figure 4 provides multi-dimensional comparison across cost and performance parameters. Higher values indicate better performance for all metrics except cost where the raw value in €/m<sup>2</sup> is shown. This visualization enables rapid identification of materials meeting specific requirement combinations, supporting informed trade-off decisions during design phase material selection.

### Comprehensive Interpretation

Regression analysis established quantitative relationships between material loss tangent and achievable data rate. The fitted model predicts maximum data rate (Gbps) = 15.2 - 580×Df with  $R^2 = 0.97$ , providing practical design guidance from material specifications [15]. This relationship enables preliminary material selection based on interface requirements without requiring detailed simulation or measurement for initial screening.

Manufacturing variation analysis revealed standard deviation in eye height of approximately 8% across specimens of the same material, indicating that nominal performance predictions should incorporate appropriate design margin. Premium materials exhibited lower variation (5-6%) attributed to tighter process control in specialty laminate production. This reduced variation provides additional benefit beyond nominal performance improvement.

### Discussion

The measured performance hierarchy aligns with theoretical predictions based on dielectric loss mechanisms. Standard FR-4 loss is dominated by dipolar relaxation in the epoxy resin system, producing the characteristic frequency-dependent loss that accelerates at higher frequencies [16]. Premium materials employ modified resin systems with reduced polar content, shifting the loss mechanism toward conductor-dominated skin effect with its more favorable frequency dependence.

The practical frequency limits identified through this research differ from theoretical calculations based on material specifications alone. Real-world performance includes contributions from surface roughness, manufacturing tolerances, and connector transitions that add loss beyond the intrinsic material properties [17]. The measured limits should therefore be considered more accurate predictors of achievable system performance than calculations from material datasheets.

Cost-benefit analysis complexity extends beyond simple material pricing to include design risk and development schedule impacts. Projects using marginally adequate materials often require multiple design iterations to achieve compliance, with each re-spin costing €50,000-€100,000 for moderately complex designs. A single avoided re-spin can justify premium material costs for thousands of production boards [18]. Risk-adjusted cost analysis therefore often favors material upgrade over aggressive cost optimization.

Limitations of this research include the focus on microstrip transmission lines without evaluation of stripline configurations that may perform differently due to more uniform dielectric environment. The 6-inch trace length tested represents typical but not universal interconnection distances; longer traces would shift material selection thresholds toward lower data rates. Future work should extend characterization to stripline structures and varied

trace lengths.

### Conclusion

This research has established quantitative relationships between PCB material properties and signal integrity performance for high-speed digital interfaces. Standard FR-4 exhibited insertion loss of 4.1 dB/inch at 10 GHz with eye height degrading below viable thresholds at 6 Gbps data rate. Rogers 4350B demonstrated lowest loss at 1.6 dB/inch maintaining adequate signal quality to 12 Gbps, representing 2.6× improvement in loss and 2× extension of viable data rate compared to standard materials.

Material cost spans a 12× range from €15/m<sup>2</sup> for standard FR-4 to €180/m<sup>2</sup> for Rogers 4350B, but cost-per-Gbps analysis reveals more nuanced value proposition. Standard FR-4 offers lowest absolute cost only for applications within its 5 Gbps capability. Applications requiring higher data rates achieve better value from premium materials that reliably support the required performance without iterative design cycles.

The regression model relating loss tangent to achievable data rate ( $R^2 = 0.97$ ) provides practical design guidance enabling material selection from specifications without requiring detailed simulation for initial screening. This relationship, combined with the measured performance limits for specific materials, establishes a quantitative foundation for material selection decisions in high-speed digital design.

Practical recommendations emerging from this research suggest standard FR-4 for interfaces operating at 5 Gbps or below, high-speed FR-4 for 5-8 Gbps applications, and premium materials for data rates exceeding 8 Gbps. The crossover point where premium materials become cost-effective depends on production volume and design complexity, but risk-adjusted analysis typically favors material upgrade over aggressive cost optimization when signal integrity margins are uncertain [19]. These guidelines enable specification-driven material selection balancing performance requirements against cost constraints for contemporary high-speed digital applications.

### Acknowledgements

#### Funding Sources

This research was supported by the Netherlands Organisation for Scientific Research through their applied electronics program and the Amsterdam Institute of Technology industry partnership initiative.

### Institutional Support

The authors acknowledge the High-Frequency Characterization Laboratory for providing measurement facilities essential to this investigation.

### Contributions Not Qualifying for Authorship

Mr. Pieter Smit provided technical assistance with test board fabrication. Dr. Anneke Visser offered consultation on statistical analysis methodology.

### References

1. Hall SH, Heck HL. Advanced signal integrity for high-speed digital designs. Hoboken: John Wiley & Sons; 2009. p. 1-45.

2. Bogatin E. Signal and power integrity simplified. 3rd ed. Boston: Prentice Hall; 2018. p. 156-198.

3. Coombs CF. Printed circuits handbook. 7th ed. New York: McGraw-Hill Education; 2016. p. 6.

4. Panasonic. Megtron 6 high-speed, low-loss multi-layer circuit board materials. Osaka: Panasonic Technical Bulletin; 2022. p. 1-12.

5. Ritchey LW. Right the first time: a practical handbook on high-speed PCB and system design. Glen Ellen: Speeding Edge; 2003. p. 89-134.

6. Rogers Corporation. RO4000 series high frequency circuit materials. Chandler: Rogers Corporation Data Sheet; 2023. p. 1-8.

7. IPC. IPC-2141A design guide for high-speed controlled impedance circuit boards. Bannockburn: IPC; 2016. p. 23-45.

8. Keysight Technologies. High-frequency structure simulator (HFSS) user guide. Santa Rosa: Keysight Technologies; 2022. p. 12.

9. IEEE. IEEE 370-2020 standard for electrical characterization of printed circuit board and related interconnects at frequencies up to 50 GHz. New York: IEEE; 2020. p. 1-156.

10. Tektronix. Eye diagram basics. Beaverton: Tektronix Application Note; 2020. p. 1-16.

11. Thierauf SC. High-speed circuit board signal integrity. Norwood: Artech House; 2004. p. 78-112.

12. Chen WK. The electrical engineering handbook. Amsterdam: Elsevier Academic Press; 2005. p. 1123-1156.

13. USB Implementers Forum. Universal serial bus 3.2 specification. Beaverton: USB-IF; 2022. p. 6.

14. PCI-SIG. PCI Express base specification revision 4.0. Beaverton: PCI-SIG; 2017. p. 8.

15. Wadell BC. Transmission line design handbook. Norwood: Artech House; 1991. p. 123-167.

16. Djordjevic AR, Sarkar TK. Closed-form formulas for frequency-dependent resistance and inductance per unit length of microstrip and strip transmission lines. IEEE Transactions on Microwave Theory and Techniques. 1994;42(2):241-248.

17. Hammerstad E, Jensen O. Accurate models for microstrip computer-aided design. IEEE MTT-S International Microwave Symposium Digest. 1980:407-409.

18. Montrose MI. EMC and the printed circuit board: design, theory, and layout made simple. Piscataway: IEEE Press; 1999. p. 145-178.

19. Johnson H, Graham M. High-speed signal propagation: advanced black magic. Upper Saddle River: Prentice Hall; 2003. p. 312-356.