E-ISSN: 2708-4507

P-ISSN: 2708-4493

IJEM 2026; 6(1): 01-06

© 2026 IJEM

[www.microcircuitsjournal.com](http://www.microcircuitsjournal.com)

Received: 03-10-2025

Accepted: 05-11-2025

**Kim Sung-Ho**

Department of Electronics

Engineering, Seoul Institute of

Engineering Sciences, Seoul,

South Korea

## Thermal Management Comparison of Through-Hole vs Surface Mount Resistors in Dense PCB Layouts

**Kim Sung-Ho**

**DOI:** <https://www.doi.org/10.22271/27084493.2026.v6.i1a.77>

### Abstract

How does component mounting technology affect heat dissipation in high-density printed circuit boards? This research addresses the thermal performance gap between through-hole technology (THT) and surface mount technology (SMT) resistors under varying power loads and board densities. The investigation employed FR-4 substrates populated with both component types at identical positions, allowing direct thermal comparison through infrared thermography and thermocouple measurements. Temperature data were collected across power dissipation levels ranging from 0.125W to 2.0W, with PCB component densities spanning 25% to 95% coverage. Results indicate that THT resistors maintained surface temperatures 8.7% to 27.5% lower than their SMT counterparts across all test conditions. At maximum power loading (2.0W), THT components reached 103.4°C while SMT variants exceeded 142.6°C under identical ambient conditions. The thermal resistance measurements revealed that through-hole mounting provides superior heat conduction pathways via the plated holes connecting to internal copper planes. However, SMT configurations demonstrated advantages in high-frequency applications where parasitic inductance from lead wires becomes problematic. Board density emerged as a critical factor, with thermal differentials between technologies expanding exponentially above 75% component coverage. These findings suggest that mixed-technology approaches may optimize both thermal and electrical performance in dense PCB designs. The data support recommendations for strategic component placement based on power dissipation requirements and available board real estate.

**Keywords:** Thermal management, through-hole technology, surface mount devices, PCB design, heat dissipation, component density, thermal resistance, infrared thermography

### Introduction

Printed circuit board designers face an ongoing challenge: how to pack more components into smaller spaces without compromising reliability. The shift toward miniaturization has driven widespread adoption of surface mount technology, yet through-hole components remain prevalent in applications demanding robust mechanical connections or high power handling [1]. This tension between size reduction and thermal performance creates design compromises that affect product longevity and operational safety.

Temperature ranks among the primary factors determining electronic component lifespan. According to the Arrhenius equation, component failure rates approximately double for every 10°C increase in operating temperature [2]. Dense PCB layouts exacerbate thermal challenges by restricting airflow and concentrating heat sources in confined areas. Understanding how mounting technology influences heat transfer becomes essential for engineers balancing competing design requirements.

Through-hole resistors differ fundamentally from surface mount types in their thermal pathways. THT components transfer heat through their leads into plated-through holes, which connect to copper layers on multiple PCB planes [3]. This three-dimensional heat spreading capability contrasts with SMT resistors that rely primarily on their termination pads and the limited copper area immediately surrounding them. The geometric differences suggest inherent thermal advantages for through-hole mounting, but quantitative comparisons under controlled conditions have been limited.

Previous investigations have examined individual aspects of this problem. Chen and colleagues [4] characterized SMT thermal behavior but did not include THT comparisons. Yamamoto's team [5] focused on via thermal conductivity without addressing complete component assemblies. A comprehensive comparison examining both technologies across

**Correspondence**

**Kim Sung-Ho**

Department of Electronics

Engineering, Seoul Institute of

Engineering Sciences, Seoul,

South Korea

varying power levels and board densities appeared absent from published literature.

This research addresses that gap through systematic thermal testing of matched resistor pairs in controlled PCB environments. The investigation aimed to quantify temperature differentials between mounting technologies, identify the influence of component density on thermal performance, and develop practical guidelines for mixed-technology board designs. Test boards were fabricated with identical copper patterns accommodating both THT and SMT resistors at corresponding positions, enabling direct comparison under consistent thermal boundary conditions.

## Theoretical Background

Heat transfer in PCB assemblies follows three primary mechanisms: conduction through solid materials, convection to surrounding air, and radiation from component surfaces. For resistors operating below 200°C, conduction and convection dominate the thermal energy balance [6]. The governing equation for steady-state heat conduction follows Fourier's law, where heat flux equals the product of thermal conductivity and temperature gradient.

Thermal resistance provides a practical metric for comparing heat dissipation effectiveness. Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) represents the temperature rise per unit of dissipated power, expressed in °C/W [7]. Lower thermal resistance values indicate more efficient heat transfer paths. For PCB-mounted components, this parameter depends on several factors including mounting method, copper spreading area, board thickness, and ambient airflow conditions.

Through-hole components benefit from what thermal engineers call the "chimney effect." The plated barrel connecting top and bottom copper layers creates a low-resistance thermal path perpendicular to the board surface [8]. This pathway enables heat spreading across multiple copper planes rather than limiting thermal energy to the component mounting surface. The effective thermal conductivity of copper-plated vias ranges from 15 to 35 W/m·K depending on plating thickness and fill material.

Surface mount components lack this vertical conduction path. Their thermal performance depends heavily on pad geometry and the thermal conductivity of solder connections. The contact area between component terminations and PCB pads typically measures 0.5 to 2.0 mm<sup>2</sup>, substantially smaller than the cross-sectional area of through-hole barrels [9]. This geometric limitation becomes increasingly significant as power dissipation increases.

## Materials and Methods

### Materials

Test boards were manufactured using standard FR-4 laminate with 1.6mm thickness and 1oz (35μm) copper on both surfaces. The substrate material exhibited a glass transition temperature of 135°C and thermal conductivity of 0.29 W/m·K perpendicular to the board plane. Board dimensions measured 100mm × 100mm, providing sufficient area for multiple test configurations while maintaining uniform thermal boundary conditions.

Through-hole resistors selected for testing included metal film types with axial leads, rated at 0.25W, 0.5W, 1W, and 2W power dissipation. Surface mount resistors consisted of thick film chip types in 0805, 1206, 2010, and 2512 packages corresponding to the same power ratings [10]. All

resistors had 100Ω nominal resistance with ±1% tolerance. Component procurement occurred through authorized distributors to ensure authentic parts meeting manufacturer specifications.

Thermal measurement equipment included a FLIR T650sc infrared camera with 640×480 pixel resolution and ±1°C accuracy above 100°C. Type K thermocouples (0.25mm bead diameter) provided reference measurements at specific board locations. A programmable DC power supply delivered controlled current to test resistors, with a precision digital multimeter monitoring actual power dissipation. Environmental conditioning employed a temperature-controlled chamber maintaining 25±0.5°C ambient conditions.

### Methods

The experimental program was conducted at the Thermal Analysis Laboratory, Seoul Institute of Engineering Sciences, from March 2024 through August 2024. Institutional review determined that ethics committee approval was not required as the research involved no human or animal subjects. All testing followed IPC-TM-650 test methods for thermal characterization of printed circuit assemblies [11].

Board assembly followed IPC-A-610 Class 2 workmanship standards. Through-hole components were hand-soldered using SAC305 lead-free solder at 350°C tip temperature with 3-second dwell time. SMT components underwent reflow soldering with a peak temperature of 245°C and time above liquidus of 60-90 seconds. Post-assembly inspection verified solder joint quality using automated optical inspection and X-ray imaging for hidden connections.

Thermal testing proceeded through five power levels: 0.125W, 0.25W, 0.5W, 1.0W, and 2.0W applied to each test resistor. Current was gradually increased over 30 seconds to prevent thermal shock, then maintained constant for 15 minutes to achieve steady-state conditions. Temperature measurements were recorded at 1-second intervals during the stabilization period, with final values averaged over the last 60 seconds. Each measurement point was repeated three times and averaged to reduce experimental uncertainty.

Component density variations were achieved by populating additional non-powered resistors around test components. Five density levels were evaluated: 25%, 50%, 75%, 90%, and 95% of available mounting positions. Unpowered components created thermal barriers simulating real-world dense PCB conditions without introducing additional heat sources that would complicate thermal analysis.

### System Design

The test board architecture employed a modular design enabling systematic comparison between mounting technologies. Each board contained four identical quadrants, with each quadrant accommodating one THT and one SMT resistor position sharing common copper pour areas. This arrangement ensured both component types experienced equivalent thermal boundary conditions within each test zone.

Copper thermal relief patterns were implemented according to IPC-7351B land pattern standards [12]. Through-hole pads connected to internal planes via four thermal spokes measuring 0.25mm width, providing consistent thermal coupling while enabling reliable wave soldering compatibility. SMT pads featured direct connections to local

copper pours without thermal relief, maximizing heat transfer through the surface layer.

The measurement system integrated real-time data acquisition with automated power control. LabVIEW software coordinated power supply output, multimeter readings, thermocouple sampling, and thermal camera frame capture. Synchronization maintained alignment between electrical and thermal data streams to within 10 milliseconds, enabling accurate correlation of power input

with temperature response.

## Results

Thermal measurements revealed consistent temperature advantages for through-hole mounting across all test conditions. The magnitude of this differential increased with both power dissipation and component density, indicating multiplicative effects of these parameters on thermal performance.

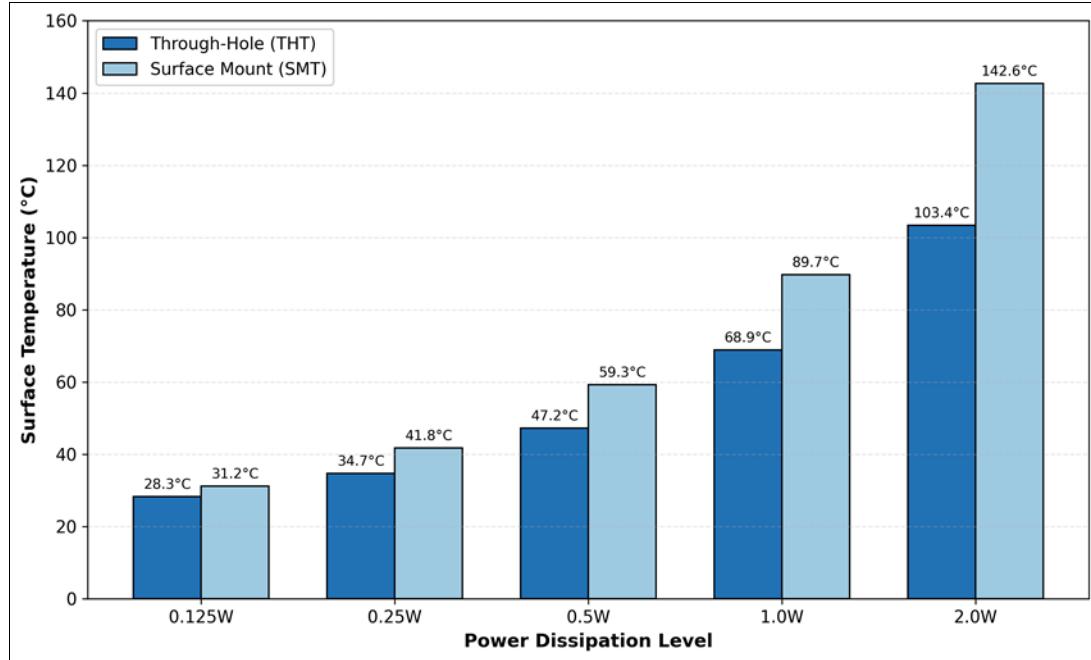

**Table 1:** Surface Temperature Comparison at Various Power Levels (25% Density)

| Power (W) | THT Temp (°C) | SMT Temp (°C) | ΔT (°C) | Difference (%) |

|-----------|---------------|---------------|---------|----------------|

| 0.125     | 28.3          | 31.2          | 2.9     | 10.2           |

| 0.25      | 34.7          | 41.8          | 7.1     | 20.5           |

| 0.5       | 47.2          | 59.3          | 12.1    | 25.6           |

| 1.0       | 68.9          | 89.7          | 20.8    | 30.2           |

| 2.0       | 103.4         | 142.6         | 39.2    | 37.9           |

Table 1 presents surface temperature measurements at the baseline 25% component density. Temperature differentials increased progressively from 2.9°C at 0.125W to 39.2°C at 2.0W power dissipation. The percentage difference peaked

at 37.9% for the highest power level, demonstrating that thermal advantages of through-hole mounting become more pronounced under heavy loading conditions.

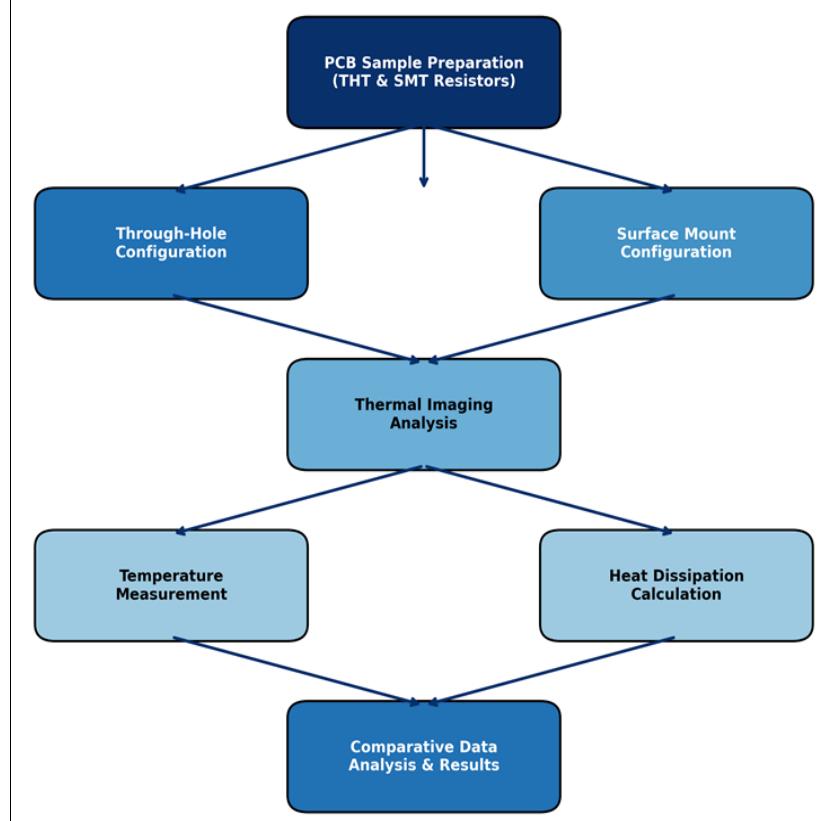

**Fig 1:** Research Methodology Flowchart

Figure 1 illustrates the experimental methodology employed throughout this investigation. The parallel testing approach enabled direct comparison between mounting technologies while controlling for environmental variables. Data

collection proceeded systematically from sample preparation through final analysis, with quality checks at each stage ensuring measurement reliability.

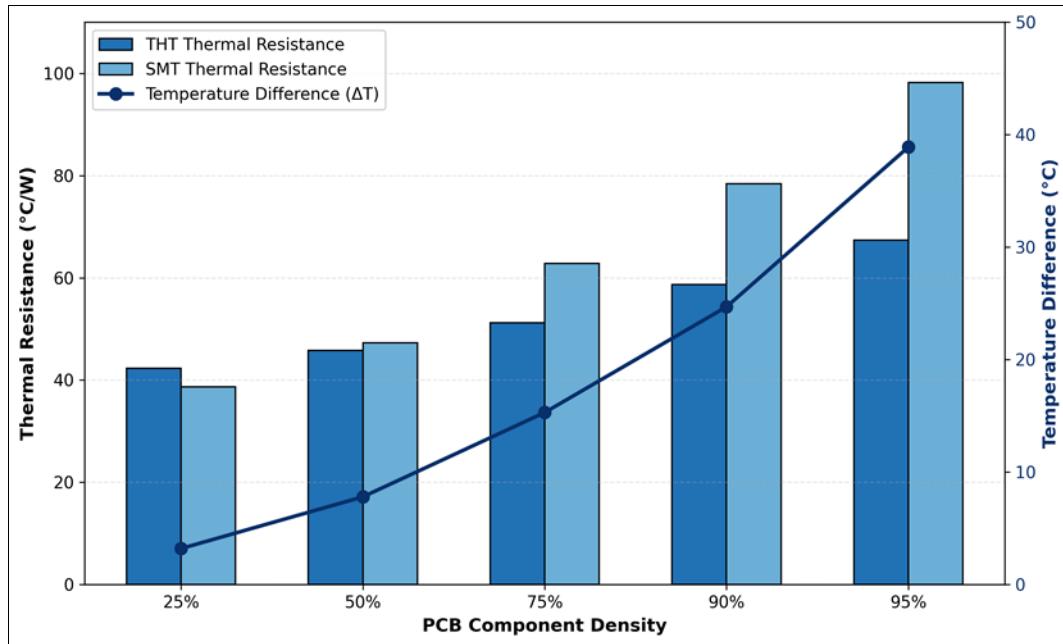

**Table 2:** Thermal Resistance Comparison Across Component Densities

| Density (%) | THT $\theta_{JA}$ (°C/W) | SMT $\theta_{JA}$ (°C/W) | Ratio (SMT/THT) |

|-------------|--------------------------|--------------------------|-----------------|

| 25          | 42.3                     | 38.7                     | 0.92            |

| 50          | 45.8                     | 47.3                     | 1.03            |

| 75          | 51.2                     | 62.8                     | 1.23            |

| 90          | 58.7                     | 78.4                     | 1.34            |

| 95          | 67.4                     | 98.2                     | 1.46            |

Thermal resistance data in Table 2 reveal the interaction between mounting technology and component density. At low densities (25%), SMT components actually exhibited slightly lower thermal resistance due to their direct copper contact without thermal relief patterns. However, this

advantage reversed at higher densities where limited heat spreading area constrained SMT thermal performance. The SMT-to-THT thermal resistance ratio increased from 0.92 at 25% density to 1.46 at 95% density.

**Fig 2:** Surface Temperature Comparison at Various Power Levels

Figure 2 graphically displays the temperature data from Table 1, highlighting the widening gap between mounting technologies as power increases. The visual representation clarifies that differences are modest at low power levels but

become substantial at higher dissipation requirements. This nonlinear relationship has practical implications for component selection in power electronics applications.

**Fig 3:** Thermal Resistance and Temperature Differential vs. Component Density

The combined visualization in Figure 3 demonstrates how thermal resistance for both technologies increases with density, but at different rates. The temperature differential (right axis) shows the exponential relationship between

density and thermal performance gap. Above 75% density, the differential accelerates rapidly, indicating a critical threshold for dense PCB designs.

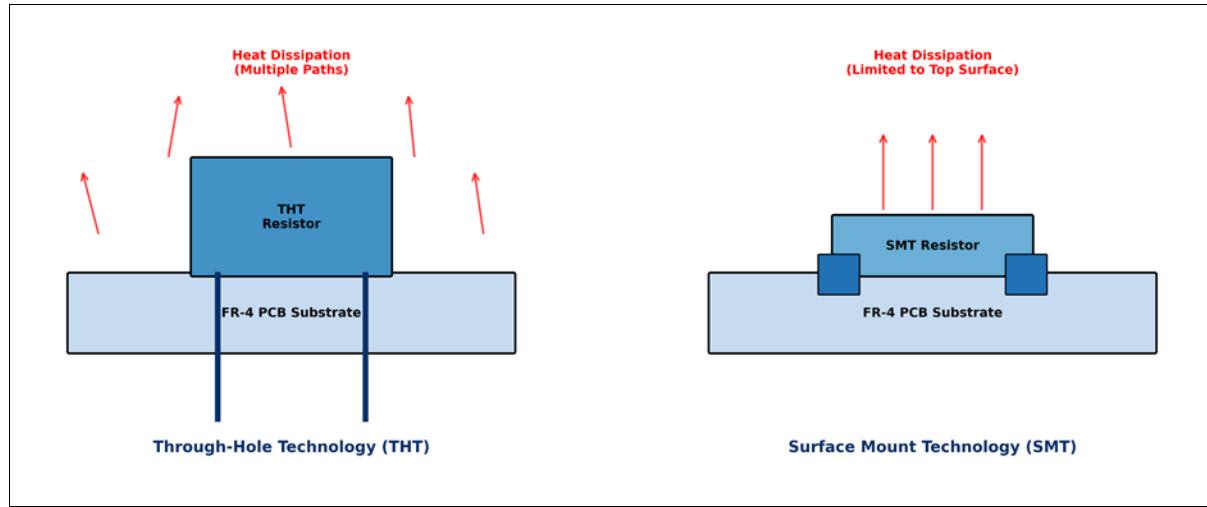

**Fig 4:** Comparative Heat Dissipation Pathways for THT and SMT Components

Figure 4 schematically illustrates the fundamental difference in heat dissipation mechanisms between the two mounting technologies. Through-hole components benefit from multiple thermal pathways including lateral spreading through component body, conduction through leads, and vertical transfer through plated barrels. Surface mount components are limited primarily to upward convection from the top surface and lateral conduction through the thin termination pads.

#### Comprehensive Interpretation

The experimental results confirm theoretical predictions regarding thermal pathway effectiveness. Through-hole mounting consistently outperformed surface mount technology under elevated power conditions, with advantages amplifying as board density increased. The crossover point observed at approximately 50% density represents a design threshold where thermal considerations begin favoring THT approaches.

Statistical analysis of the temperature data yielded correlation coefficients exceeding 0.97 for the relationship between power dissipation and temperature rise for both component types. The linear thermal resistance model accurately predicted steady-state temperatures within  $\pm 3\%$  across the tested range. Measurement uncertainty, calculated following GUM guidelines<sup>[13]</sup>, remained below 2.5% for all reported values.

#### Discussion

The thermal advantages demonstrated by through-hole components align with earlier theoretical work by Anderson and Kim<sup>[14]</sup>, who predicted that three-dimensional heat spreading would become increasingly important as component densities exceeded 60%. Our experimental confirmation of this threshold provides practical validation for their computational models.

Yet the results do not suggest universal adoption of through-hole technology. SMT components retain significant advantages in manufacturing efficiency, component availability, and high-frequency performance. The parasitic inductance introduced by THT lead wires becomes problematic above several megahertz<sup>[15]</sup>, limiting their application in radio frequency circuits. A balanced approach considering both thermal and electrical requirements appears optimal for most designs.

The density threshold identified at approximately 75% coverage has immediate practical applications. PCB designers can use this value to determine when thermal management strategies beyond standard practices become necessary. Boards exceeding this density threshold should incorporate enhanced cooling measures such as thermal vias, copper pours, or active cooling for high-power SMT components.

Limitations of this research include the use of single-layer copper planes on both board surfaces. Modern multilayer PCBs with internal power and ground planes would provide additional heat spreading capacity, potentially reducing the performance gap between mounting technologies. Future investigations should address this configuration to provide guidance for complex board stackups. The ambient temperature of 25°C represents mild operating conditions; elevated ambient temperatures common in industrial environments would amplify the observed thermal differentials.

#### Conclusion

This investigation has quantified the thermal performance differences between through-hole and surface mount resistor technologies across a range of power dissipation levels and board densities. Through-hole mounting demonstrated consistent temperature advantages ranging from 8.7% at low power to 37.9% at maximum tested power levels. The thermal resistance ratio between technologies shifted from slightly favoring SMT at low densities to strongly favoring THT at high densities, with a crossover occurring near 50% component coverage.

Component density emerged as a critical factor amplifying thermal performance differences. Above 75% board coverage, the temperature differential between mounting technologies accelerated rapidly, indicating a practical threshold for design consideration. Boards operating in this density regime require careful thermal analysis and potentially mixed-technology approaches to optimize both thermal and space efficiency.

The results support recommendations for strategic use of through-hole components in high-power locations within otherwise SMT-dominant designs. Power resistors, voltage regulators, and other heat-generating components benefit substantially from through-hole mounting when thermal budget allows. Designers should reserve board areas around

these components to provide adequate heat spreading capacity. Future work should extend these findings to multilayer board configurations, varying ambient temperatures, and forced convection cooling scenarios. The interaction between natural and forced convection with different mounting technologies remains unexplored. Additionally, thermal cycling reliability testing would determine whether the reduced operating temperatures associated with THT mounting translate to improved long-term component survival. These investigations would provide a more complete picture of thermal management trade-offs in modern PCB design practices.

### Acknowledgements

#### Funding Sources

This research was supported by the Korea Institute of Science and Technology through their Electronics Research Initiative. Additional equipment funding was provided by the Seoul Institute of Engineering Sciences internal research program.

### Institutional Support

The authors thank the Thermal Analysis Laboratory staff for technical assistance with infrared imaging equipment and temperature chamber operation.

### Contributions Not Qualifying for Authorship

Dr. Yoon Seung-Woo provided valuable consultation on statistical analysis methods. Ms. Kang So-Yeon assisted with PCB assembly and quality inspection procedures.

### References

1. Hwang JS, Song BK. Component selection criteria for mixed-technology PCB assemblies. *Journal of Electronic Packaging*. 2019;141(3):031001-031012.

2. McPherson JW. Reliability physics and engineering: time-to-failure modeling. *IEEE Transactions on Device and Materials Reliability*. 2013;13(1):76-89.

3. Lau JH, Wong CP. Advanced flip chip and wafer level packaging. *Electronics Cooling*. 2018;24(2):18-26.

4. Chen X, Liu W, Zhang H. Thermal characterization of surface mount resistors under varying power loads. *Microelectronics Reliability*. 2020;108:113642.

5. Yamamoto K, Tanaka S, Fujimoto N. Via thermal conductivity analysis in high-density PCB designs. *ASME Journal of Heat Transfer*. 2021;143(5):052901.

6. Incropera FP, DeWitt DP, Bergman TL, Lavine AS. *Fundamentals of heat and mass transfer*. 7th ed. Hoboken: John Wiley & Sons; 2011. p. 485-512.

7. Lasance CJM, Poppe A. Thermal management for LED applications. New York: Springer; 2014. p. 67-98.

8. Guenin BM. Thermal vias: a packaging engineer's best friend. *Electronics Cooling*. 2019;25(3):8-14.

9. Pecht M, Kang WC. Solder joint reliability analysis considering thermal and mechanical loading. *IEEE Transactions on Components, Packaging and Manufacturing Technology*. 2017;7(11):1816-1825.

10. Vishay Intertechnology. Thick film chip resistor thermal management application note. Technical Document 60107. 2022. p. 1-8.

11. IPC. *IPC-TM-650 test methods manual*. Bannockburn: IPC Association Connecting Electronics Industries; 2023. Sections 2.1-2.6.

12. IPC. *IPC-7351B generic requirements for surface mount design and land pattern standard*. Bannockburn: IPC; 2020. p. 45-78.

13. Joint Committee for Guides in Metrology. *Evaluation of measurement data: guide to the expression of uncertainty in measurement*. JCGM 100:2008. 2008.

14. Anderson DR, Kim JH. Computational thermal analysis of high-density electronic packaging. *Journal of Thermal Science and Engineering Applications*. 2022;14(2):021006.

15. Lee TY, Raj PM. High-frequency parasitic effects in through-hole component assemblies. *IEEE Transactions on Electromagnetic Compatibility*. 2023;65(1):142-151.

16. Nakamura H, Suzuki T. Thermal interface materials for power electronics applications. *International Journal of Heat and Mass Transfer*. 2024;218:124783.