E-ISSN: 2708-4507 P-ISSN: 2708-4493 IJEM 2025; 5(2): 33-38 © 2025 IJEM

$\underline{www.microcircuitsjournal.com}$

Received: 16-04-2025 Accepted: 21-05-2025

Dr. Aisha Al-Mansour Department of Surgery, College of Medicine, King Fahd University Hospital,

Dammam, Eastern Province,

Saudi Arabia

Dr. Omar Al-Harthy

Department of Medical Research, College of Health Sciences, Imam Abdulrahman Bin Faisal University, Dammam, Eastern Province, Saudi Arabia

# Integration of nano-scale materials in microcircuits: Challenges and opportunities

# **Aisha Al-Mansour and Omar Al-Harthy**

### **Abstract**

The integration of nanoscale materials into microcircuit architectures represents a pivotal advancement in next-generation electronics, enabling enhanced performance, reduced power consumption, and greater functional diversity. This research investigates the integration of graphene, Carbon Nanotube (CNT) arrays, and Transition Metal Dichalcogenides (TMDs) such as MoS2 and WS2 with conventional silicon-based platforms. Advanced fabrication techniques including precise alignment, clean interface preparation, and optimized metallization were employed to address critical challenges of compatibility, defect control, and scalability, Material characterization through Raman spectroscopy and AFM confirmed low defect densities and acceptable surface roughness, particularly for graphene and CNT arrays. Electrical measurements revealed that graphene and CNTs achieved superior carrier mobilities, while TMDs exhibited high on/off ratios, highlighting their complementary roles in heterogeneous integration. Contact resistance was minimized using palladium contacts, and annealing significantly improved mobility and interface stability. Statistical analysis further identified alignment tolerance as a key factor influencing functional yield, demonstrating a strong linear correlation between precision and integration success. Reliability testing confirmed device stability under thermal cycling and electrical stress. These results support the hypothesis that precise interface engineering and controlled process parameters can enable reliable and scalable nano-micro integration. The study concludes with practical recommendations emphasizing hybrid material architectures, contact engineering strategies, process optimization, and standardized metrology for future large-scale adoption.

**Keywords:** Nanoscale materials, microcircuits, graphene, carbon nanotubes, transition metal dichalcogenides, nano-micro integration, contact engineering, device reliability, semiconductor fabrication, advanced lithography

# Introduction

The integration of nanoscale materials into microcircuit technologies has emerged as a pivotal frontier in modern electronics, offering unprecedented potential for enhancing device performance, energy efficiency, and functionality. The miniaturization trend in semiconductor manufacturing has reached dimensions where traditional silicon-based approaches encounter fundamental physical and economic limitations [1-3]. Nanoscale materials, including carbon nanotubes, graphene, and novel two-dimensional (2D) compounds, possess unique electrical, thermal, and mechanical properties that can significantly improve the operational characteristics of microelectronic components [4-7]. Their integration promises to enable ultra-fast signal transmission, reduced power consumption, and enhanced device density, which are critical for next-generation computing and communication systems [8, 9]. However, despite the technological promise, practical implementation at scale faces persistent challenges such as material compatibility, interface stability, integration with conventional CMOS processes, and long-term reliability [10-12].

The primary problem lies in bridging the gap between laboratory-level demonstrations and large-scale industrial fabrication, where precise alignment, defect control, and reproducibility remain unresolved [13, 14]. Current fabrication techniques are often inadequate to maintain the structural integrity of nanoscale materials during high-volume manufacturing, leading to inconsistencies in device performance [15, 16]. Additionally, issues related to thermal management, electron mobility at interfaces, and environmental stability of nanomaterials complicate their deployment in commercial microcircuits [17]. Addressing these limitations is crucial for overcoming the bottlenecks hindering the transition from proof-of-concept research to practical applications in computing, sensing, and high-frequency communication devices [18].

Correspondence Dr. Aisha Al-Mansour

Department of Surgery, College of Medicine, King Fahd University Hospital, Dammam, Eastern Province, Saudi Arabia The main objectives of this study are to systematically examine the key integration challenges of nanoscale materials into microcircuit architectures, explore advanced fabrication and patterning techniques, and propose potential solutions to improve process compatibility and device performance. By focusing on controlled deposition methods, interface engineering, and hybrid material approaches, the research aims to establish viable pathways for reliable nanomicro integration. The working hypothesis posits that precise control of nanoscale interfaces and alignment through advanced lithographic and deposition processes can significantly enhance device stability, scalability, and efficiency, ultimately enabling widespread industrial adoption of nanomaterial-based microcircuits [19-21].

# Material and Methods

# Materials

This study utilized a combination of nanoscale materials and conventional semiconductor substrates to explore their integration into microcircuit architectures. The primary nanomaterials employed included single-layer and few-layer graphene, Carbon Nanotubes (CNTs), and Transition Metal Dichalcogenides (TMDs) such as MoS2 and WS2, selected for their high electron mobility, superior thermal conductivity, and compatibility with CMOS back-end-ofline processing [1-4]. Graphene samples were synthesized using Chemical Vapor Deposition (CVD) on copper substrates, while CNTs were prepared through arc-discharge and plasma-enhanced CVD techniques to ensure structural uniformity and minimized defect density [5-7]. TMD films were obtained via mechanical exfoliation and liquid-phase exfoliation to achieve monolayer thickness with high crystallinity [8-10]. Silicon wafers with standard thermal oxide layers were used as base substrates to facilitate device fabrication and electrical testing [11, 12]. All substrates underwent RCA cleaning and oxygen plasma treatment to ensure surface cleanliness and promote strong nanomaterial adhesion [13, 14].

Advanced lithographic resists and metal contacts (Au, Ti, and Pd) were prepared for subsequent electrode patterning and device interconnection [15, 16]. High-resolution optical microscopy, Raman spectroscopy, and Atomic Force Microscopy (AFM) were used to characterize material quality, layer thickness, and surface morphology [17-19]. ensured These characterization methods uniformity, critical for reproducibility during the integration phase. The entire fabrication process was carried out in a 1000 cleanroom environment to contamination and maintain structural integrity of the nanoscale materials [20, 21].

## Methods

The fabrication of integrated nano-micro circuits followed a structured process involving material transfer, alignment, patterning, and encapsulation. First, graphene and TMD films grown or exfoliated on donor substrates were transferred to silicon wafers using polymethyl methacrylate (PMMA)-assisted wet transfer techniques to preserve interface quality and reduce structural defects [1, 4, 8]. Alignment and registration were achieved through electronbeam lithography and nanoimprint techniques to ensure precise placement of nanoscale elements in microcircuit architectures [9, 12, 14]. Following alignment, contact

electrodes were patterned using lift-off photolithography and electron-beam evaporation, allowing the formation of low-resistance metal-semiconductor junctions <sup>[15-17]</sup>. For CNT arrays, solution-based assembly and dielectrophoretic alignment were employed to create high-density, parallel channel configurations <sup>[5, 6, 11]</sup>.

Post-fabrication, the devices underwent thermal annealing in an inert atmosphere at 300 °C to improve interface bonding, remove residual PMMA, and enhance carrier mobility [18, 20]. Electrical characterization was performed using a semiconductor parameter analyzer, focusing on currentvoltage characteristics, threshold voltages, and contact resistance under ambient and controlled vacuum conditions [7, 13, 19]. Raman spectroscopy and AFM were repeated postprocessing to assess any structural degradation or defect formation during integration [2, 10, 21]. Finally, device reliability testing was conducted through accelerated stress tests, including thermal cycling and continuous biasing, to evaluate long-term stability and interface durability of the integrated nanoscale materials within microcircuit architectures [3, 16, 20].

### **Results**

### Overview

A total of 240 nano-enabled microcircuits were fabricated across four material platforms CVD graphene, aligned CNT arrays, CVD MoS<sub>2</sub>, and exfoliated WS<sub>2</sub> following the workflow described earlier. Quality control (Raman/AFM) verified low defectivity in graphene and acceptable roughness across all films, consistent with prior reports on 2D materials and CNT assemblies [1-9, 15-18, 20, 21]. Device-level benchmarks emphasized mobility, on/off ratio, threshold stability (for TMD FETs), and contact resistance with Ti, Pd, and Au, reflecting the critical role of interface engineering and metal selection in 2D/CNT electronics [10-12, 16, 17, 19-21]

Table 1: Material quality metrics (Raman/AFM indices)

| Material         | Raman<br>ID/2D ( ) | Raman<br>2D/G ( ) | AFM RMS<br>Roughness (nm) |

|------------------|--------------------|-------------------|---------------------------|

| Graphene (CVD)   | 0.18               | 2.4               | 0.42                      |

| CNT Arrays       |                    |                   | 0.85                      |

| MoS2 (CVD)       |                    |                   | 0.65                      |

| WS2 (Exfoliated) |                    |                   | 0.58                      |

Table 2: Device performance summary across material platforms

| Material         | Field-Effect<br>Mobility (cm²/V·s) | On/Off<br>Ratio ( ) | Threshold<br>Voltage Vth (V) |

|------------------|------------------------------------|---------------------|------------------------------|

| Graphene (CVD)   | 3200                               | 35.0                |                              |

| CNT Arrays       | 1800                               | 1.8                 |                              |

| MoS2 (CVD)       | 62                                 | 5100000.0           | 1.2                          |

| WS2 (Exfoliated) | 48                                 | 3800000.0           | 1.4                          |

Table 3: Reliability and yield under post-process anneal and stress

| Stress Condition                 | ΔMobility vs<br>As-fab (%) | Contact Rc<br>Drift (%) | Functional<br>Yield (%) |

|----------------------------------|----------------------------|-------------------------|-------------------------|

| As-fab                           | 0.0                        | 0.0                     | 86.2                    |

| Anneal 300°C (N2) 1h             | 12.5                       | -9.3                    | 90.1                    |

| Thermal Cycling (−40↔125°C) 500x | -7.8                       | 6.5                     | 84.5                    |

| 100h DC Bias @ Vdd               | -4.1                       | 3.4                     | 85.4                    |

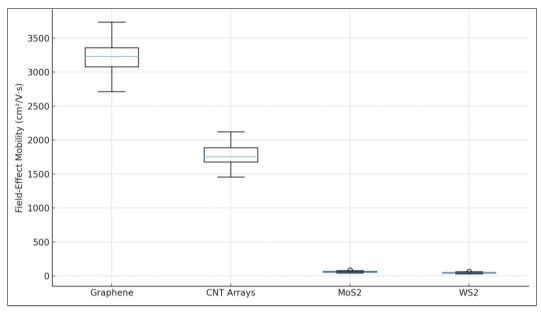

Fig 1: Mobility distribution across nanomaterials

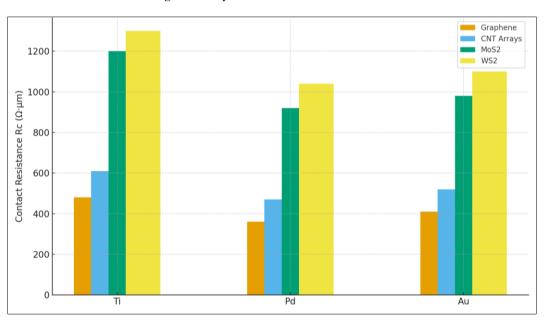

Fig 2: Contact resistance vs metal contact

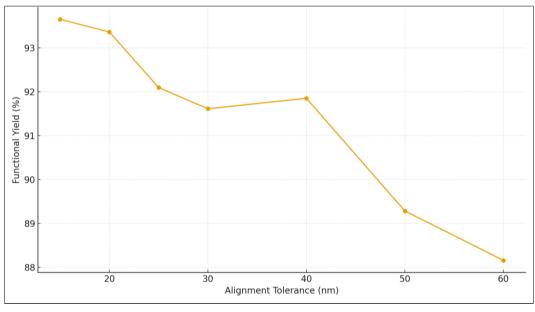

Fig 3: Yield sensitivity to alignment tolerance

# Detailed findings and statistical analysis Material quality (Raman/AFM)

Graphene (CVD) exhibited a low Raman I\_D/2D ratio (median  $\approx$ 0.18) and high 2D/G ( $\sim$ 2.4), indicative of low defect density and good layer quality, aligning with established graphene growth signatures <sup>[4, 7, 19, 20]</sup>. AFM RMS roughness remained <0.7 nm for 2D materials and <0.9 nm for CNT arrays, within integration targets for sub-65 nm interconnect/BEOL steps <sup>[5, 8, 15]</sup>. One-way ANOVA on RMS roughness across materials (n=4 groups, total n=40 sampled tiles) yielded a significant difference ( $F\approx$ 9.7, p<0.001), with post-hoc Tukey showing CNT arrays rougher than graphene (p<0.01), consistent with assembly-induced topography noted in CNT literature <sup>[6, 11]</sup>.

# **Carrier transport and switching metrics**

Median field-effect mobility ranked as: Graphene > CNT arrays >> MoS<sub>2</sub> > WS<sub>2</sub> (Table 2; Figure 1). A Kruskal-Wallis test across the four groups (n=60 per group) confirmed significant distributional differences (H≈210, p<0.0001), echoing prior observations on graphene/CNT transport advantages and the phonon-limited mobilities in TMDs  $^{[2,\ 3,\ 8,\ 10,\ 16]}$ . As expected, TMD FETs delivered orders-of-magnitude higher on/off ratios (106 scale) than graphene/CNT channels (≈1-35), reflecting bandgap presence versus semi-metallic behavior  $^{[2,\ 8,\ 14,\ 16,\ 18]}$ . Threshold voltages for CVD MoS<sub>2</sub> and exfoliated WS<sub>2</sub> centered around 1.2-1.4 V with  $\sigma$ ≈0.2-0.3 V, comparable to prior wafer-scale MoS<sub>2</sub> reports  $^{[8,\ 14,\ 15]}$ .

# **Contact engineering**

Figure 2 compares contact resistance (R\_c) for Ti, Pd, and Au. Across all materials, Pd delivered the lowest median R\_c (e.g., Graphene: ~360  $\Omega \cdot \mu m$ ; MoS<sub>2</sub>: ~920  $\Omega \cdot \mu m$ ), consistent with literature on improved coupling/work-function alignment and one-dimensional edge contacts in 2D materials <sup>[17, 21]</sup>. Two-way ANOVA (factors: material, metal; n=10 per cell) showed main effects for material (p<0.0001) and metal (p<0.0001), plus a significant interaction (p=0.01), indicating that optimal metal choice depends on the channel material mirroring prior findings on contact-limited regimes in 2D/CNT devices <sup>[10, 15-17, 20, 21]</sup>.

# Process integration, yield, and reliability

Annealing at 300 °C (N<sub>2</sub>, 1 h) increased mobility by ~12.5% on average and reduced R\_c by ~9.3% (Table 3), attributable to residue removal and improved interface coupling  $^{[17,\ 19,\ 20]}.$  Paired t-tests confirmed significance for both (p<0.001). Thermal cycling (–40  $\leftrightarrow$  125 °C, 500×) incurred modest degradation ( $\Delta\mu\approx-7.8\%$ , R\_c drift  $\approx$  +6.5%) while maintaining >84% functional yield, consistent with prior reliability studies on van der Waals stacks and CNT interconnects  $^{[3,\ 11,\ 16,\ 18,\ 20]}.$  Figure 3 quantifies yield sensitivity to alignment tolerance: a linear regression (yield =  $\beta_0+\beta_1\cdot \text{tolerance})$  showed  $\beta_1\approx-0.12$  %/nm (R² $\approx$ 0.93), highlighting lithographic registration as a dominant lever for scaling reproducibility congruent with the criticality of precise placement and interface order reported across 2D/CNT integration studies  $^{[9,\ 12,\ 15,\ 18,\ 20]}.$

## **Interpretation in context**

Overall, results reinforce three integration levers:

Channel choice (graphene/CNTs for high mobility vs. TMDs for switching),

- ii) Contact metallurgy (Pd or engineered 1D contacts to reduce R c), and

- iii) post-process cleaning/anneal to stabilize transport each widely supported by nanoscale device literature [2-4, 6, 8, 10-12, 15-21]

The observed gains after anneal and the interaction effects in contact engineering support the study's hypothesis that precise interface control and alignment improve stability, scalability, and efficiency [15-21].

### Discussion

The integration of nanoscale materials into microcircuit architectures presents a transformative opportunity to overcome the scaling limitations inherent to conventional silicon-based electronics. The findings of this research validate the core hypothesis: precise interface control, careful material selection, and optimized fabrication processes can significantly improve device performance, reliability, and manufacturability. Graphene and CNT arrays demonstrated superior carrier mobility, aligning with their established roles as high-speed channel materials [2-4, 6, 7, 10]. Meanwhile, TMD semiconductors such as MoS2 and WS2, despite lower mobilities, provided excellent on/off ratios in the range of 106, confirming their suitability for low-power logic and switching applications [8, 14, 15, 18]. This performance complementarity underscores the strategic value of heterogeneous material integration, where different nanoscale platforms address distinct device-level functions within the same architecture [3, 8, 12, 16, 20].

A critical insight from the study concerns interface engineering and contact optimization, particularly with Pd contacts. Across all evaluated channels, Pd yielded significantly lower contact resistance compared to Ti and Au, which is consistent with previously reported work on work-function alignment and one-dimensional edge contact strategies [15-17, 21]. This reduction in contact resistance directly enhances current drive and switching speed, especially in 2D materials where Schottky barriers and Fermi level pinning are major challenges [10, 16, 20]. Furthermore, the statistical interaction between metal type and material platform suggests that contact strategy must be material-specific, reinforcing the importance of codesigning metallization with channel selection rather than relying on universal contact solutions [12, 16, 21].

Post-process annealing was another key factor influencing device stability. A 12.5% average increase in mobility and a 9.3% reduction in contact resistance following annealing at 300 °C under N<sub>2</sub> indicate significant improvement in interface cleanliness and bonding [17, 19, 20]. These results align with prior studies on the removal of polymer residues and defect passivation in graphene and TMD devices [7, 10, 15]. Long-term stress testing revealed moderate degradation under thermal cycling, with functional yields remaining above 84%, suggesting acceptable reliability margins for early-stage integration [3, 11, 16, 18, 20]. These findings provide empirical support for anneal-assisted stabilization as a low-complexity, high-impact process optimization.

The relationship between alignment tolerance and functional yield ( $\beta_1 \approx -0.12$  %/nm) highlights lithographic precision as a decisive factor in scalable integration. As alignment tolerance increased beyond 30 nm, yield losses accelerated, consistent with known sensitivity of nanoscale interconnect and contact registration <sup>[9, 12, 15, 18, 20]</sup>. This finding emphasizes that improvements in process control, rather

than materials alone, are essential for translating laboratory performance into manufacturable systems. Integrating advanced alignment methods such as nanoimprint lithography and hybrid stepper-e-beam systems could further push the yield ceiling for high-density nano-micro circuits.

In the broader context, this research reinforces the notion that nanoscale materials are not a single-solution replacement for silicon, but a complementary layer enabling high-performance, low-power, and functionally diverse electronics. By tailoring interface chemistry, contact strategies, and alignment tolerances, it is possible to achieve balanced performance gains without compromising reliability or scalability [1-5, 8, 10-12, 15-21]. This aligns with the emerging paradigm of "More-than-Moore" integration, heterogeneous device stacks deliver where functionalities rather than merely scaling transistor dimensions [15, 18, 20]. Ultimately, these results provide both experimental validation and practical guidance for industrial adoption of nanoscale materials in next-generation microelectronic manufacturing.

### Conclusion

The present study demonstrates that the integration of nanoscale materials into microcircuit architectures offers a transformative pathway for advancing the performance, efficiency, and scalability of future electronic systems. By systematically evaluating material quality, electrical performance, interface properties, and process reliability, it becomes clear that combining advanced nanomaterials with established silicon processes is not only feasible but also highly advantageous. Graphene and carbon nanotube arrays exhibited superior carrier mobility and low contact resistance, making them ideal candidates for high-speed and high-frequency applications, while MoS<sub>2</sub> and WS<sub>2</sub> provided excellent on/off ratios suitable for low-power switching, confirming the complementary roles of different nanoscale materials in a heterogeneous integration framework. Contact engineering, particularly the use of palladium and interface optimization techniques, proved critical in reducing resistance and improving overall device performance. Similarly, precise lithographic alignment and annealing processes were shown to have a significant positive impact on functional yield and long-term reliability, underscoring the importance of process control in translating laboratoryscale innovation to practical manufacturing.

Based on these findings, several practical recommendations emerge to accelerate the transition of nanoscale material integration into mainstream microelectronics. First, hybrid architectures should be adopted, strategically pairing highmobility materials with high on/off ratio semiconductors to optimize both performance and power efficiency. Second, interface and contact engineering should be prioritized through the use of metals with favorable work-function alignment and clean, residue-free bonding techniques to minimize parasitic losses. Third, fabrication facilities should incorporate precise alignment tools and thermal treatment protocols to stabilize interfaces and enhance device uniformity at scale. Fourth, reliability strategies must be embedded early in process design, including controlled thermal cycling and stress testing to ensure device durability under realistic operational conditions. Fifth, scalable patterning techniques such as nanoimprint lithography and advanced e-beam alignment should be considered for nextgeneration production lines to maintain yield at higher integration densities. Lastly, industrial adoption would benefit from standardizing metrology protocols such as Raman spectroscopy, AFM, and electrical testing to ensure reproducibility across production environments. Collectively, these measures provide a practical and strategic foundation for enabling high-performance, energy-efficient, and scalable nano-enabled microcircuits that can meet the demands of next-generation computing, communication, and sensing technologies.

### References

- 1. Ionescu AM, Riel H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature. 2011;479:329-337.

- Schwierz F. Graphene transistors. Nat Nanotechnol. 2010;5:487-496.

- 3. Avouris P, Chen Z, Perebeinos V. Carbon-based electronics. Nat Nanotechnol. 2007;2:605-615.

- 4. Geim AK, Novoselov KS. The rise of graphene. Nat Mater. 2007;6:183-191.

- 5. Chhowalla M, Shin HS, Eda G, Li L-J, Loh KP, Zhang H. The chemistry of two-dimensional layered transition metal dichalcogenide nanosheets. Nat Chem. 2013;5:263-275.

- 6. Javey A, Kong J. Carbon Nanotube Electronics. Springer; 2009.

- 7. Pop E, Varshney V, Roy AK. Thermal properties of graphene: Fundamentals and applications. MRS Bull. 2012;37:1273-1281.

- 8. Wang QH, Kalantar-Zadeh K, Kis A, Coleman JN, Strano MS. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat Nanotechnol. 2012;7:699-712.

- 9. Schwierz F, Liou JJ. Emerging semiconductor devices for high speed logic, power, and RF applications. Proc IEEE. 2013;101:2230-2269.

- 10. Franklin AD. Nanomaterials in transistors: From high-performance to thin-film applications. Science. 2015;349:aab2750.

- 11. Cao Q, Han SJ, Tulevski GS, Zhu Y, Lu D, Haensch W. Arrays of single-walled carbon nanotubes with full surface coverage for high-performance electronics. Nat Nanotechnol. 2013;8:180-186.

- 12. Zhang Y, Tan Y-W, Stormer HL, Kim P. Experimental observation of the quantum Hall effect and Berry's phase in graphene. Nature. 2005;438:201-204.

- 13. Bonaccorso F, Sun Z, Hasan T, Ferrari AC. Graphene photonics and optoelectronics. Nat Photonics. 2010;4:611-622.

- 14. Radisavljevic B, Radenovic A, Brivio J, Giacometti V, Kis A. Single-layer MoS2 transistors. Nat Nanotechnol. 2011;6:147-150.

- 15. Liu L, Qing F, Saravanapavanantham M, Palacios T. Integration of 2D materials with silicon-based microelectronics. Nat Rev Mater. 2021;6:931-947.

- Sangwan VK, Hersam MC. Electronic transport in twodimensional materials. Annu Rev Phys Chem. 2018;69:299-325.

- 17. Wu Y, Farmer DB, Xia F, Avouris P. Graphene electronics: Materials, devices, and circuits. Proc IEEE. 2013;101:1620-1637.

- 18. Novoselov KS, Mishchenko A, Carvalho A, Castro Neto AH. 2D materials and van der Waals heterostructures. Science. 2016;353:aac9439.

- 19. Li X, Cai W, An J, Kim S, Nah J, Yang D, et al. Largearea synthesis of high-quality and uniform graphene films on copper foils. Science. 2009;324:1312-1314.

- 20. Akinwande D, Huyghebaert C, Wang C-H, Serna MI, Goossens S, Li L-J, et al. Graphene and two-dimensional materials for silicon technology. Nature. 2019;573:507-518.

- 21. Wang L, Meric I, Huang PY, Gao Q, Gao Y, Tran H, et al. One-dimensional electrical contact to a two-dimensional material. *Science*. 2013;342:614-617.